Rambus Announces Industry-First HBM4 Controller IP to Accelerate Next-Generation AI Workloads

Rambus Inc. (NASDAQ: RMBS) has announced the industry's first HBM4 Memory Controller IP, expanding its leadership in high-bandwidth memory solutions. This new controller supports JEDEC Spec of 6.4 Gbps and can operate up to 10 Gbps, delivering a throughput of 2.56 TB/s per memory device. It's designed to meet the demanding memory bandwidth requirements of next-generation AI accelerators and GPUs.

The HBM4 Controller IP aims to address the growing needs of Large Language Models (LLMs) and high-performance computing (HPC) applications. It builds on Rambus' track record of over 100 HBM design wins and can be paired with third-party or customer PHY solutions. The controller is now available for licensing, with early access design customers able to engage immediately.

Rambus Inc. (NASDAQ: RMBS) ha annunciato il primo IP del Controller HBM4 del settore, ampliando la sua leadership nelle soluzioni di memoria ad alta larghezza di banda. Questo nuovo controller supporta la specifica JEDEC di 6,4 Gbps e può operare fino a 10 Gbps, offrendo una capacità di elaborazione di 2,56 TB/s per dispositivo di memoria. È progettato per soddisfare le esigenti necessità di larghezza di banda di memoria dei futuri acceleratori AI e GPU.

L’IP del Controller HBM4 mira a rispondere alle crescenti esigenze dei Modelli Linguistici di Grandi Dimensioni (LLM) e delle applicazioni di calcolo ad alte prestazioni (HPC). Si basa sull’esperienza di Rambus con oltre 100 vittorie nel design HBM e può essere abbinato a soluzioni PHY di terze parti o di clienti. Il controller è ora disponibile per la licenza, con i clienti di design a accesso anticipato che possono interagire immediatamente.

Rambus Inc. (NASDAQ: RMBS) ha anunciado el primer IP del Controlador HBM4 de la industria, ampliando su liderazgo en soluciones de memoria de alto ancho de banda. Este nuevo controlador soporta la especificación JEDEC de 6,4 Gbps y puede operar hasta 10 Gbps, ofreciendo un rendimiento de 2,56 TB/s por dispositivo de memoria. Está diseñado para satisfacer las exigentes necesidades de ancho de banda de memoria de los futuros aceleradores de IA y GPU.

El IP del Controlador HBM4 tiene como objetivo abordar las crecientes necesidades de los Modelos de Lenguaje de Gran Escala (LLMs) y aplicaciones de computación de alto rendimiento (HPC). Se basa en el historial de Rambus con más de 100 diseños ganadores de HBM y puede ser emparejado con soluciones PHY de terceros o del cliente. El controlador ya está disponible para licencias, con clientes de diseño de acceso anticipado que pueden participar de inmediato.

램버스 주식회사 (NASDAQ: RMBS)는 업계 최초의 HBM4 메모리 컨트롤러 IP를 발표하며 고속 메모리 솔루션에서의 리더십을 확장했습니다. 이 새로운 컨트롤러는 JEDEC 규격 6.4 Gbps를 지원하며 최대 10 Gbps로 작동할 수 있어, 메모리 장치당 2.56 TB/s의 처리를 제공합니다. 이는 차세대 AI 가속기 및 GPU의 엄격한 메모리 대역폭 요구를 충족하도록 설계되었습니다.

HBM4 컨트롤러 IP는 대규모 언어 모델(LLM)과 고성능 컴퓨팅(HPC) 애플리케이션의 증가하는 요구를 해결하는 것을 목표로 합니다. 이는 램버스가 100개 이상의 HBM 디자인 승리를 거둔 경험을 바탕으로 하며, 제3자 또는 고객의 PHY 솔루션과 결합할 수 있습니다. 이 컨트롤러는 이제 라이선스가 가능하며, 초기 접근 설계 고객들이 즉시 참여할 수 있습니다.

Rambus Inc. (NASDAQ: RMBS) a annoncé le premier IP de Contrôleur HBM4 de l'industrie, élargissant sa leadership dans les solutions de mémoire à haute bande passante. Ce nouveau contrôleur prend en charge la spécification JEDEC de 6,4 Gbps et peut fonctionner jusqu'à 10 Gbps, offrant un débit de 2,56 To/s par dispositif de mémoire. Il est conçu pour répondre aux exigences rigoureuses de bande passante mémoire des accélérateurs IA et GPU de nouvelle génération.

L'IP du Contrôleur HBM4 vise à répondre aux besoins croissants des Modèles de Langage de Grande Taille (LLM) et des applications de calcul haute performance (HPC). Il s'appuie sur le bilan de Rambus avec plus de 100 succès en conception HBM et peut être associé à des solutions PHY de tiers ou de clients. Le contrôleur est maintenant disponible pour licence, avec des clients de conception d'accès anticipé pouvant s'engager immédiatement.

Rambus Inc. (NASDAQ: RMBS) hat den ersten HBM4-Speichercontroller IP der Branche angekündigt und damit seine Führungsposition im Bereich hochbandbreitiger Speicherlösungen ausgebaut. Dieser neue Controller unterstützt die JEDEC-Spezifikation von 6,4 Gbps und kann bis zu 10 Gbps betrieben werden, wobei er eine Durchsatzrate von 2,56 TB/s pro Speichergerät liefert. Er ist darauf ausgelegt, die anspruchsvollen Anforderungen an die Speicherbandbreite von Next-Generation KI-Beschleunigern und GPUs zu erfüllen.

Der HBM4-Controller IP zielt darauf ab, den wachsenden Bedürfnissen von Large Language Models (LLMs) und Hochleistungsrechenanwendungen (HPC) gerecht zu werden. Er baut auf Rambus' Erfolgsbilanz mit über 100 gewonnenen HBM-Designs auf und kann mit PHY-Lösungen von Dritten oder Kunden kombiniert werden. Der Controller ist jetzt zur Lizenzierung verfügbar, mit frühzeitigen Designkunden, die sofort teilnehmen können.

- First-to-market with HBM4 Memory Controller IP, reinforcing industry leadership

- Supports up to 10 Gbps operation, providing 2.56 TB/s throughput per memory device

- Addresses growing memory bandwidth needs for AI and HPC applications

- Built on a proven track record of over 100 HBM design wins

- Available for immediate licensing with early access for design customers

- None.

Insights

Rambus' introduction of the industry-first HBM4 Controller IP marks a significant leap in memory technology for AI and HPC applications. This development is crucial for addressing the escalating memory bandwidth demands of large language models and complex AI workloads. The controller's ability to support up to 10 Gbps, delivering a throughput of

The strategic importance of this release lies in its potential to unlock new levels of AI performance, particularly for training and inference tasks. By alleviating memory bottlenecks, Rambus is positioning itself as a key enabler in the AI hardware ecosystem. The broad industry support, including collaborations with Samsung and Cadence, suggests a strong market potential for HBM4 technology.

For investors, this positions Rambus favorably in the rapidly growing AI chip market, potentially leading to increased market share and revenue growth in the coming years.

Rambus' HBM4 Controller IP release is a strategic move that solidifies its position in the high-performance memory solutions market. With over 100 HBM design wins, Rambus leverages its expertise to address a critical need in the AI and HPC sectors. The timing is impeccable, as it coincides with the industry's shift towards more complex AI models requiring unprecedented memory bandwidth.

The interoperability with third-party PHY solutions enhances the IP's versatility, potentially accelerating adoption across various chip designs. This flexibility could translate into a wider customer base and increased licensing revenues for Rambus. Moreover, by offering early access to design customers, Rambus is fostering early adoption and establishing itself as the go-to provider for HBM4 solutions.

Investors should note that this development positions Rambus at the forefront of the next wave of AI hardware innovation, potentially leading to long-term growth opportunities in the semiconductor IP space.

The introduction of Rambus' HBM4 Controller IP is a game-changer for AI accelerator and GPU designs. By doubling the throughput of HBM3 while maintaining low latency, this technology addresses a critical performance bottleneck in AI systems. The capability to support up to 10 Gbps operation is particularly noteworthy, as it provides headroom for future performance scaling.

For AI workloads, especially those involving trillion-parameter models, this advancement could translate to significant reductions in training time and improved inference speeds. The potential impact on real-time AI applications is substantial, possibly enabling more complex models to run efficiently on edge devices.

From an investment perspective, Rambus is now well-positioned to capitalize on the growing demand for high-bandwidth memory solutions in the AI sector. The company's first-mover advantage in HBM4 technology could lead to increased market share and potentially higher profit margins as AI hardware manufacturers race to incorporate the latest memory advancements in their designs.

Highlights:

- Built on a proven track record of over one hundred HBM design wins to ensure first-time silicon success

- Delivers more than double the throughput of HBM3 at low latency to meet the demands of Generative AI & High-Performance Computing (HPC) workloads

- Expands industry-leading silicon IP portfolio of high-performance memory solutions

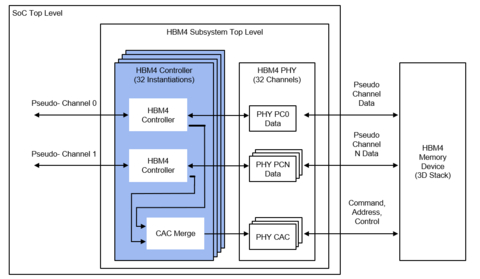

Rambus HBM4 Controller (Graphic: Business Wire)

“With Large Language Models (LLMs) now exceeding a trillion parameters and continuing to grow, overcoming bottlenecks in memory bandwidth and capacity is mission critical to meeting the real-time performance requirements of AI training and inference,” said Neeraj Paliwal, SVP and general manager of Silicon IP, at Rambus. “As the leading silicon IP provider for AI 2.0, we are bringing the industry’s first HBM4 Controller IP solution to the market to help our customers unlock breakthrough performance in their state-of-the-art processors and accelerators.”

“As heterogenous compute architectures are implemented at an ever-increasing scale to support a wide range of workloads with tremendous amounts of data movement, it is essential that the HBM IP ecosystem continues to extend performance and deliver interoperable solutions to meet the growing needs of customers,” said Arif Khan, senior group director of protocol IP marketing in the Silicon Solutions Group at Cadence. “We are pleased to see Rambus offer an interoperable HBM4 Controller IP solution to support the ecosystem alongside Cadence’s leadership in HBM PHY and solutions performance once the industry transition to this new generation of HBM memory begins.”

“HBM4 will represent a major advancement in memory technology for generative AI and other HPC applications,” said Jongshin Shin, executive vice president and head of Foundry IP Ecosystem at Samsung Electronics. “The availability of HBM4 IP solutions will be critical to paving the path for widespread HBM4 adoption in the market and Samsung looks forward to collaborating closely with Rambus and the wider ecosystem to develop new HBM4 solutions for the AI era.”

“In today’s complex and fast-paced semiconductor design landscape, pre-validated IP solutions are key to achieving first-time silicon success,” said Abhi Kolpekwar, vice president and general manager, Digital Verification Technology division, Siemens Digital Industries Software. “Rambus and Siemens have a long-standing and successful collaboration to help our mutual customers meet their product and business goals, and we look forward to working together to deliver a new generation of best-in-class Rambus HBM4 memory controllers verified with Siemens’ high-quality Verification IP.”

“HBM is a key enabling technology for AI because AI processors and accelerators need high-performance, high-density memory for the massive computational requirements of AI workloads," said Shane Rau, Research VP for Computing Semiconductors at IDC. "As AI processors and accelerators advance, they will need HBM to advance, too. Seeing HBM4 IP in the market now is a key enabling building block that will be ready for designers working on cutting-edge AI hardware."

The Rambus HBM4 Controller enables a new generation of HBM memory deployments for cutting-edge AI accelerators, graphics and HPC applications. The HBM4 Controller supports the JEDEC Spec of 6.4 Gigabits per second (Gbps). The Controller is further capable of supporting operation up to 10 Gbps providing a throughput of 2.56 Terabytes per second (TB/s) to each memory device. The Rambus HBM4 Controller IP can be paired with third-party or customer PHY solutions to instantiate a complete HBM4 memory subsystem.

Availability and More Information:

The Rambus HBM4 Controller IP is the latest addition to the Rambus leading-edge portfolio of digital controller solutions. The Controller is available for licensing, and early access design customers can engage today.

Learn more about the Rambus HBM4 Controller IP at https://www.rambus.com/interface-ip/hbm/.

The HBM4 memory standard is in development by JEDEC. JEDEC standards are subject to change during and after the development process, including disapproval by the JEDEC Board of Directors.

Follow Rambus:

Company website: rambus.com

Rambus blog: rambus.com/blog

X/Twitter: @rambusinc

LinkedIn: www.linkedin.com/company/rambus

Facebook: www.facebook.com/RambusInc

About Rambus Inc.

Rambus is a provider of industry-leading chips and silicon IP making data faster and safer. With over 30 years of advanced semiconductor experience, we are a pioneer in high-performance memory solutions that solve the bottleneck between memory and processing for data-intensive systems. Whether in the cloud, at the edge or in your hand, real-time and immersive applications depend on data throughput and integrity. Rambus products and innovations deliver the increased bandwidth, capacity and security required to meet the world’s data needs and drive ever-greater end-user experiences. For more information, visit rambus.com.

Forward-looking statements

Information set forth in this press release, including statements as to Rambus’ outlook and financial estimates and statements as to the expected timing and effects of Rambus products, constitute forward-looking statements within the meaning of the safe harbor provisions of the Private Securities Litigation Reform Act of 1995.

These statements are based on various assumptions and the current expectations of the management of Rambus and may not be accurate because of risks and uncertainties surrounding these assumptions and expectations. Factors listed below, as well as other factors, may cause actual results to differ significantly from these forward-looking statements. There is no guarantee that any of the events anticipated by these forward-looking statements will occur, or what effect they will have on the operations or financial condition of Rambus. Forward-looking statements included herein are made as of the date hereof, and Rambus undertakes no obligation to publicly update or revise any forward-looking statement unless required to do so by federal securities laws.

Major risks, uncertainties and assumptions include, but are not limited to: any statements regarding anticipated operational and financial results; any statements of expectation or belief; other factors described under "Risk Factors" in Rambus’ Annual Report on Form 10-K and Quarterly Reports on Form 10-Q; and any statements of assumptions underlying any of the foregoing. It is not possible to predict or identify all such factors. Consequently, while the list of factors presented here is considered representative, no such list should be considered to be a complete statement of all potential risks and uncertainties.

Source: Rambus Inc.

View source version on businesswire.com: https://www.businesswire.com/news/home/20240909968582/en/

Cori Pasinetti

Rambus Corporate Communications

t: (650) 309-6226

cpasinetti@rambus.com

Source: Rambus Inc.