DNP Develops Interposer, a Primary Component in Next-Generation Semiconductor Packaging

Dai Nippon Printing Co., Ltd. (DNP) has developed a new interposer, a high-performance device that connects multiple chips, set to enhance next-generation semiconductor packaging. This innovation addresses the challenges of increased wiring resistance and insulation degradation. Participating in the JOINT2 consortium, DNP is targeting mass production by 2024, focusing on improving semiconductor functionality. This move aligns with the industry’s push for higher density chip integration, aiming to overcome the limitations of traditional miniaturization processes.

- Development of a high-performance interposer to enhance semiconductor packaging.

- Participation in JOINT2 consortium targeting mass production in 2024.

- Focus on improving functionality and integrating multiple chips.

- High costs and complexity in miniaturization are approaching limits.

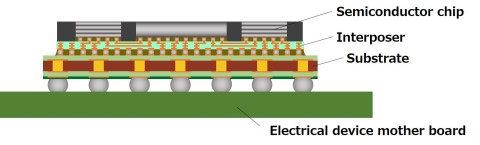

Layer Structure (Graphic: Business Wire)

DNP also has participated in Jisso Open Innovation of Tops 2 (JOINT2), targeting further functional developments for mass-production in 2024. JOINT2 is a consortium comprising 12 companies developing semiconductor packaging materials, substrates, and equipment.

“Through cooperation with the other participating JOINT2 companies, DNP will accelerate the further functionality of the interposer as well as advance initiatives aimed at mass production in 2024. We will also promote the development of next-generation semiconductor packaging technology.” says

Background

The shift to higher functionality, greater speed and lower power consumption for semiconductor products requires miniaturization technology of semiconductor by using photo-lithography. It is said, however, that further miniaturization is rapidly approaching its limit, due to the complexity of the process and high costs. To overcome these challenges, the focus is on next-generation semiconductor packaging technology that improves processing speed by mounting multiple chips (e.g., CPUs, AI processors and memories) at high-densities, on the surface of an interposer.

Features

The interposer overcomes the issue of an increase in wiring resistance, and degradation of insulation resistance between the wirings, to achieve the high-performance necessary for leading edge semiconductor packaging.

DNP manufactures templates for nanoimprint lithography, a next-generation pattern transfer technology by employing microfabrication technology based on printing processes. We also broadly expand businesses through MEMS foundry services for sensors. In this latest development, we have applied glass and silicon substrate processing developed through the aforementioned businesses for advanced packaging technologies, along with handling technology and fine wiring formation technology.

About DNP

Since 1876, DNP is a global leader in the provision of printing solutions that connect people and society, providing new value. We exploit our proprietary strengths in printing and information to propose solutions that support the development of a people-friendly information society, including electronic components targeting next-generation communications, and platforms that boost IoT information security.

https://www.dnp.co.jp/eng/news/detail/10161795_2453.html

View source version on businesswire.com: https://www.businesswire.com/news/home/20211207005066/en/

DNP:

kitagawa-y3@mail.dnp.co.jp

Source:

FAQ

What is the new development by Dai Nippon Printing (DNPLY) related to semiconductors?

When does Dai Nippon Printing expect to achieve mass production of the interposer?

What is the purpose of the interposer developed by DNP?

What consortium is DNP participating in for semiconductor advancements?